are

TPIS

199.

Al C

operational amplifies (cor) Typical amplifier:

non-inventing of sweets is gone of on to tolary? He sate to Level & Killing Mage inverting

tent-go an to ellinger priplique

ge

Lat

58

nput

This

-> Aditi amp is basically the 1/p stage of an ampropriation

->An operamp obrivatated as op amp is versatile electronice it device whochfinds to many app practical applications.

- An operational amp is basically very high gain direct coupled amp with high 1/p impedence and low offimpedence

-> the block diagram of op-amp as shown in fig. from the block dragram it is seen that the ilp stage employes a dual ilp balanced ofp stage diff amp which provider a major parts of the voltage gain and high ilp siesistance.

-) This can be applied intermediate stage which in another dual ilp balanced of ditt amp. Since the ilp stage amp and intermediate alage amp one dinect coupled. So the De voltage at the olp of an intermediate stage gives sitse to above the ground which Is not designable.

-): To bringing the DC voltage down to O. A level skufter cor) this is coually an enotifer follower. It acts translator is used

www.Jntufastupdates.com

Scanned by CamScanner

as buffer with large isp impedence and low olp impedence. william transferigo

- -) The ofp stage contains a complementary symmetry push pull amp which helps to increase the old voltage swing, and the crossent supplying capacity of an op-amp,

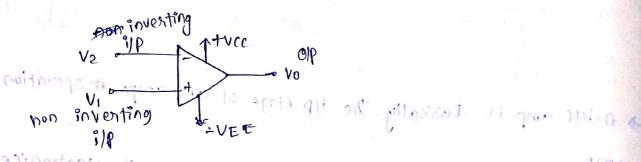

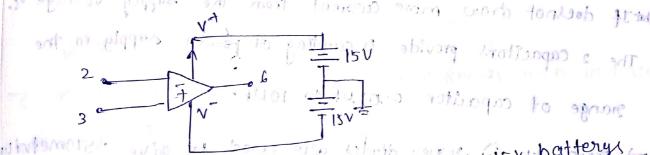

- -) The ckil symbol of an op-amp is shown in fig-

-) let the ilp voltager vi and v2 we apply at the noninverting and investing terminals respectively of an op-any let vo denotes an olp vollage we have to

Vos A (Vi-v2) o omobogos que desta atropa que balques where A is the diff gain of an op-amp

-) If the inventing ip terminal is grounded ie, V2 so and The votage. V1 is applied then we

have Vo = AV1 -> similarly the non inverting 1/p terminal inground is i.e, Vi=0 the voltage V2 is applied the when have afor medicate stage amp rose direct rou

wear of of an intermediate stage gives some to go and the

characteristics of ideal and practical op-ampi-- An ideal op-amp exhibits the following characteristics 1) voltage gain pis asimilant ban pritieren est die starrous ii) The ip impedence is do iii) The old impedence is o \_ał iv) The Brw is do. -> when equal Voltages are applied at the two i/p terminals 5 tet Deland Tes denote he current to the Olp is 7010. -) There is no change in the characteristic features with changes R biomed. of temperature. the order of Pris mano ampo - where as inpractical op - amp the voltage gain is large and very high ilp impedence and very low olp impedence and off -) A small olp voltage appears even when equal voltages are applied at the thoo i/p terminals. i/p offset voltage!--) It is defined as the voltage that heeds to be applied across the flp terminals of an opamp in order to cause the o/p 33 voitage to becomes 700. - In other woords it is the voltage which must be applied blw nput the inverting and non inverting terminal to null the op. (بر -) It is generally in the order of few microvolts. This RS Nio = Vdc1 - Vdc2

3

1/POFF set currently to latting han hall to without

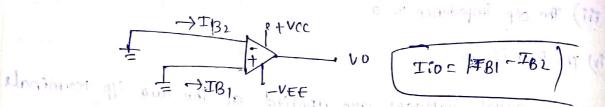

-) It is defined as the algebric difference blue The Currents into the investing and noninverting if terminals of an op-amp. It is denoted by I'm

- Let IB, and IBI denote The currents which thow into the i/p terminals in the transistors one peroperly biased

-) where I've is the order of few nano ampers.

Ilp bias current the real provider another is apply

-) It is defined as the mean of the current that flow into The investing and noninvesting terminals of an op-amp. It is denoted by IB.

- It is usually in the order of few nano ampere-

where IBI and IB2 are the base consients of transistors of the 1st stage.

Ofp Offset Voltage: -

The voltage which appears as o/p for & ?/p. is termed as old off set voltage. It is denoted as voos!

Vios Adel - Ages -

slew state: - It is detirned as the max state of change of olp voltage for unit time.

The slew state of an op-amp is an important parameter grait is a measure of ability of ap-amp to handle all varying signals.

Supply voltage Rejection ratio (SVRR) cos) power supply RR (of PSRR It is defined as the matio of change in ilp of the let voltage to the change in supply voltage is termed as supply voltage rejection matio.

-) since large changes i/p and off offset voltages effects

the performance of op-amp. So it is desirable at SVRR

as low as possible.

Jet can be also expensed in OB

drift Cor) thermal denist:

5

Bias current, offset current, off set voltage change with temperature. A ckt carefully nulled at 25°C.

may not remain so when the temperature gives to 35°C.

This called doift.

Mak

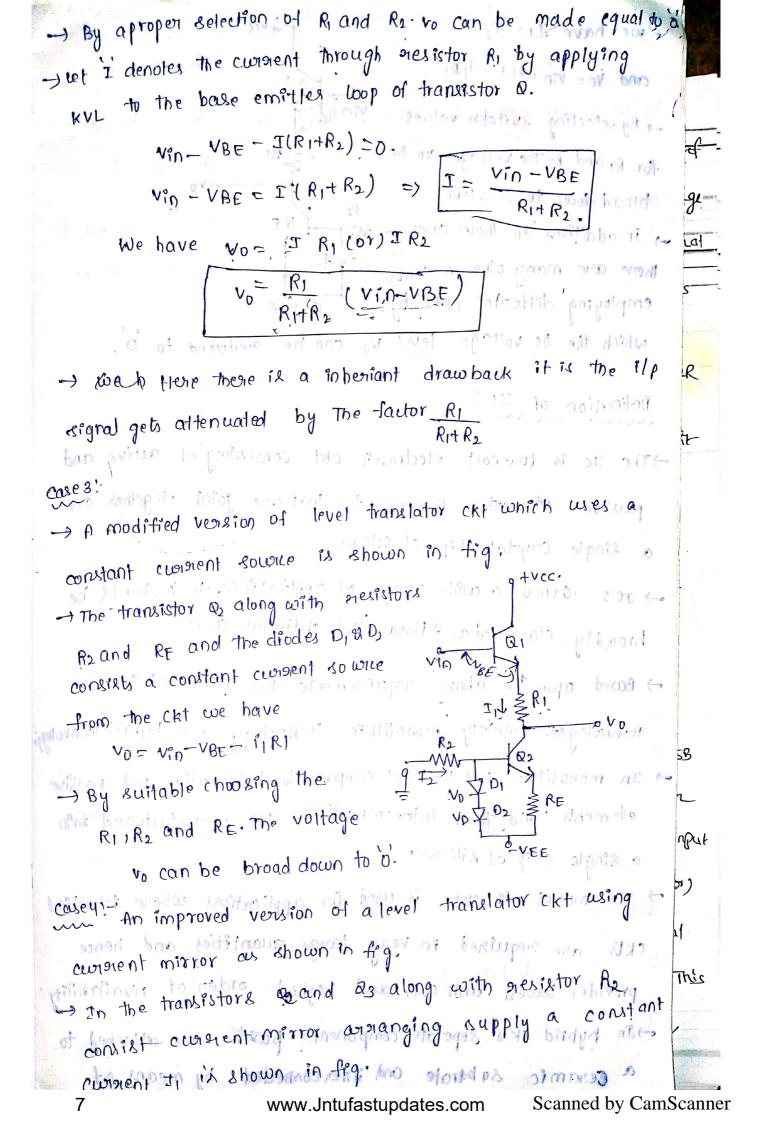

-) often ilp offset consient in nanoamperes/oc voltage uv/°c. The Offset drift measured in level translator: (or) level shiften! -> The level translator is basically an emitted follower inquitors parameter cose! - In this case the simplest version of level translator which consists of an emitter follower with fixed sies nesiston R'in the nanying gapani. -4V(C emitter ckt. power supply RP (of PINA 01 or pringer of angodination -) let vin denotes the DC voltage level of the old of intermed stage prieceiding level shifter stage. Jf vo is old voltage we have vor vin - VBE FO - Oil of the state of Vo = Vin - D. A brought prod aros 6 brought down by abor -> By using level shifter the Do level can be 0.7V' case?: In practice the sieduction of Dc Voltage level may prove be impossible. In order to further bring down the volta level to practically o . The above ckt is modified a show in figure. trcc -) Resistor R is supplaced by Resistors Roand Re joined as The Design of the Miles ghown in figure. - The old is taken blow the function point of RIIR2 and the ground

we have II = I2

and Vo = Vin - VBE - i1 R1

-1 By selecting suitable values vin hazes

for R1 and R2 the voltage can be

broad down to zero level.

In additions to these cases

there are many other methods

employing different ckts by

d-VEE

which the Dc voltage level vo can be reduced to O.

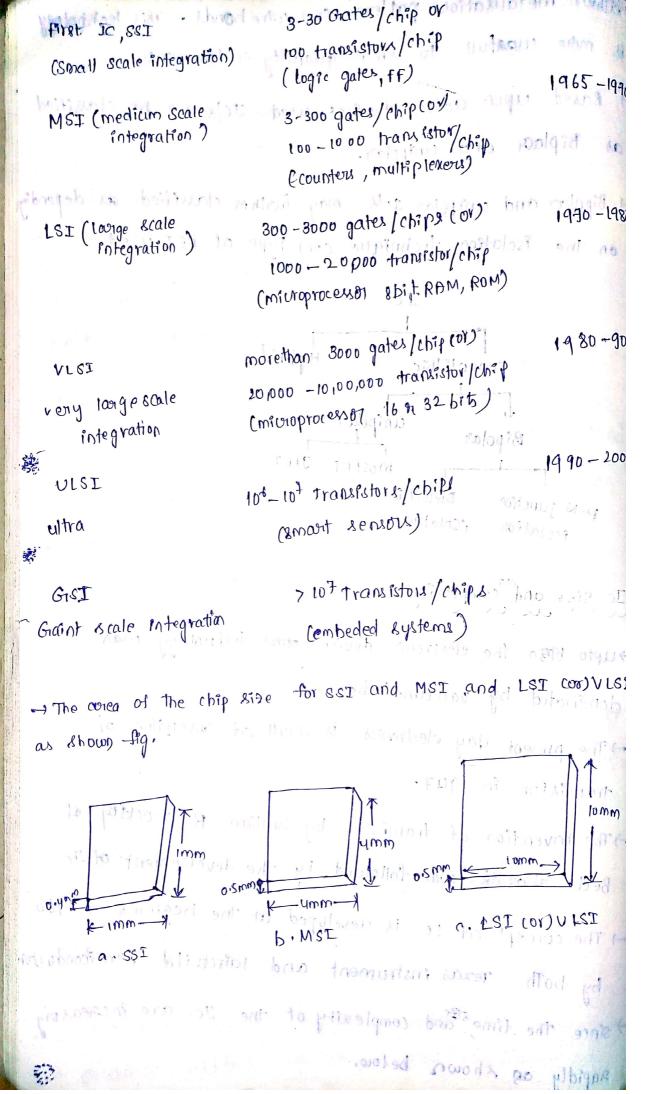

Defination of IC: 14 rotal and pd

The Ic is low cost electronic ckt consisting of active and possive edements: components that are joint together on a single crystal chip of silicon.

stand gets attenuated

- broadly classified as i) linear Icls 2) digital Icls

- → Based upon the above nequinements two different Ic technological namely monolithic technology and hybrid technology

- In monolithic Icls all ckt components both active and passive elements and their interconnections are manufactured into a single chip of silicon.

- The monolithic ckt is used for applications where idential ckts are nequined in very large quantities and hence provides lowest unit cost and highest order of Availability In hyprid ckts reperate component parati are attached to

a Benamic subtrate and interconnected by means of

Based was Biplan

on the Ps

either meta

P-H Jun

Je Size of which will be seen and the seen and the seen and the seen are seen as a seen are seen are seen as a seen are seen are seen as a seen are seen are seen as a seen are seen as a seen are seen are seen are seen as a seen are seen

transis.

The Po

Bell

→ The c

-) since sapid

either metalisation pattern con wire bonds. This technology to small quantity custom City: cuspatull 15 more - Based It's can be classified upon active devices used Biplan and unipolar. as - Bipologi and unipologi Icls may fronth ex classified as depending ge isolation technique cor, type of FET used. lat on the (mindicemen sty Bull 60. monolithic LR unipolasioniquem) tt-Bipolon JFET MOSFET USI Dielectric rotalennit of the PN Junction i'solations sease troops ortho rsolation Ic size and complexity is most 1210 Whiteholas old -> upto 1950 the electronic device was technology dominated by vaccume tubes and some part out to man out to -> The present day electronics is negult of invention of (do) of 8 do SB transistor in 1947. -The Provention of transistor by William Bishockly of mput Beil laboration was followed by the development of Ic 7) - The concept of Ic is developed at the begining of 1960 1 by both texas instrument and fairchild semiconductor This I since the time stand complexity of the Ic are increasing sapidly as shown below. Scanned by CamScanner 9 www.Jntufastupdates.com

To packages there wie three popular available packages.

- ti metalean packages! mod actionals rotaves redana

- pins is called the investing ropul demorrals . 2. Dual In line (DIP)

- The off terminal and the planet of 7 package.

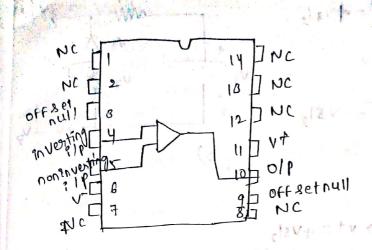

dominated. -> op - amp packages may contains single, dual, town op-amp fipical packes have 8 terminals, nou terminals 14 terminals, widely used very popular. It is

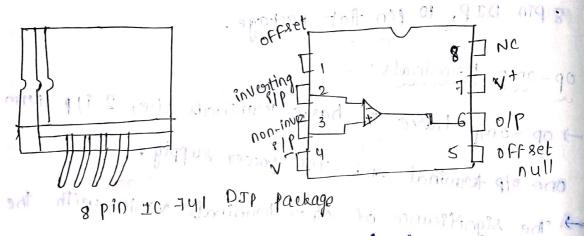

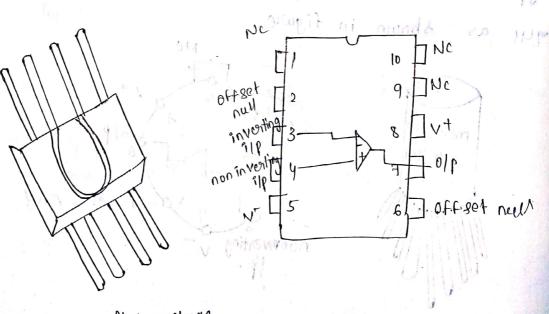

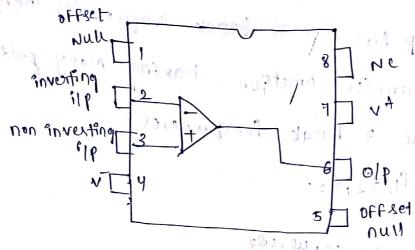

-) Ic's 741 and is available has 8 pin metal can, 8 pin DIP, 10 lin flat package.

op-amp terminals. -

-) op -amp have 5 basic terminals i.e. 2 ilp terminals one of terminal and two power supply.

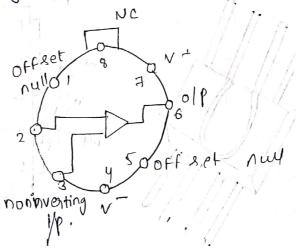

-> The significance of other terminals varies with the of op-amp. The metal can package the are

shown in figure.

16 pin flat portage

rat

LR

SB

nput

0)

41

The metal can package top view of ICFUI has a spining with pin are the pin number 8. Identified by tap. The other pin are number counter clockwise from pins begining with pining pins is called the inverting input terminal. Pin 6 ls the olp terminal and the pin 4 of 7 vcc power supply terminals. Tabelled as v & v respectively terminals terminals. Tabelled as v & v respectively terminals. I abelled as v & pins marked as the pins marked as

-) The IC 741 DIP Package as shown in figure.

-) A pin 10 pin Hat package shown in figr

power supply connection!

V+, V- power supply terminals are connected to -) The 2 nc voltage sources. The v+ pin connected to the . tre terminal of I source. The v-terminal is connected to -ve terminal of another source.

From the figure the two sources are isvibatterys each of these are the typical values but in general the powen supply vollage may may mange from ±5V to ± 22V;

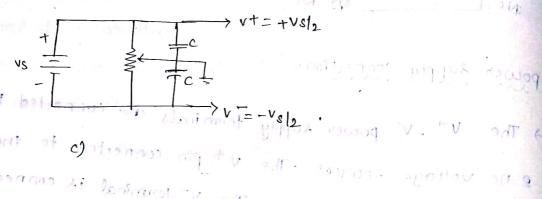

The common terminal of the v+ and v- sources is connected to ground Instead of curing 2 power supplies (- 0) power supply we obtain vtandv we can use 1 single bet org as shown inckts.

rat

LR.

it

SB

input

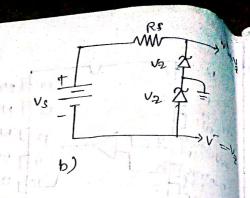

R should be greater than toka. -) from figure @ The resistor R should that if doesnot draw more awner from the supply voltage v. The 2 Capacitors provide D coupling of power supply in the siange of capcuitor oxplut to 10Mf.

-) from ck1- 6) zener diodes are cused to give symmetric eupply voltages. The value of the Rs is choosen such that It supplies sufficient convents from the Zener diodes to operate in the avalaunche mode. The plant reason

-> from fig @ potention eter is used to get equal values of v+ and v- the diodes Drand Dr is used rome. one con elle paingle pour protect the Ic.

mang

giange

manufa

> Each specifi

- For manu

-) Here

Fair

The Conn for

1. fo

2,

4.

5.8

7.

of shown inckti.

open loop ap - amp configuration:

-) open loop means there is no interconnection blw 3/p and olp terminals re, there is no feed back from o/p to the 14 -) The open loop op-amp configurations can be widely category into 3 types. songe o lo acie/acr.

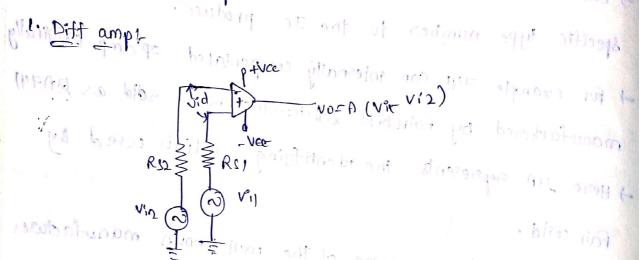

1. Differential amp

?. inverting amp

3. noninverting amp

Vil and viz exeperesents the ilp signal of inventing and nominvesting i/p terminals. we have the olp voltage vo=A(virviz) where A siepsiesents open loop op amp gain.

· bless rist

where vid = Vi1 - Viz 7 m

-: dwo bullengis tomostane donot . d

-) let the noninventing ilp terminal be grounded the we have the Olp voltage Vos-Aus

- From this relation we can said that there adation inversion to discould have the operated 3. noninverting amp; 8+VCC 19d YEUR A playing rat 2R In a noninverting amplifier there is no phase difference such an amp is shown in fig. the ilp andopvoltages it -) The inventing ilp terminal is grounded the signal vite is applied at the non inverting terminal. 1-e v12=0. -) The tre sine of old voltage implies that there is no -Priversion blw ofprostage and PIP voltage. frequency Response of op-amp! SB magnitude plot ojain rob 0.70Th input 096 B.W . For (0) frequippedi st 17 al and the product of goin, and by phase plot This 10 as to atop spottov

17

-> The open loop voltage gain of an op-amp curi is the matio of olp voltage to the differential ip voltage reproduced my how

gone following

ice,

$$AOL = \frac{VO}{Vid}$$

- -) The gain is purely a number being the ratio of evoltages however The gain can be usually expressed in decibals

- .. Voltage gain = 20/09/10 (vod) dB.

- The gain of an op-amp is a not ofixed magnitude But it is frequency dependent The gain changes with the change of frequency of the flp signal.

- -) This change of voltage gain with change of frequency t all entrovai off is termed as frequency response of an op-omp

- -) The Graphical suppresentation of variations of gain with frequency is could frequency response choive (or) F. R. (harack - Stic curve.

- Stic curve.

The frequency response curve as slown in tig. from the tig. Fo is the corner frequency cor) Break frequency

- -) The B.W = Fo 0 = FO HZ where ft is the gain Brow product

- -) It is defined as the product of gain and Bow the voltage gain of an op-amp is a complex quantity having both magnitude and phase at f=0 The magnitude of

satio or n

nges

The

y

is max and the phase shift is ac.

- at F= Fo The corner frequency. The gain is 3dB lessthan gain at F=0. and phase shift is -45°.

- -) It is seen than the curve to beyond the corner frequency ge to the gain devicases almost linearly with w. sito trequent

- -) The slope of the linear part of the curve 20 dB for decapade.

- -) The Reduction of gain is with increase of signal frequency can be explain as follows

- thom the chi we are use only a copacitive sauthly -> An op-amp mainly consisting of BJT (ov) FET transist and these transistors having & Junction transistor.

- -) The impedence offered by a capacitance is given by Xc= 27tfet

- -> It is obvious that x yarious inversity with frequency of at low frequencies xc is very large, and capacitor act on open ckt.

- The higher frequencies the impodence of the capacitance input peromes quiet small Due to the effect of capacitanto, the voltage gain reduces. al

- In addition to the internal capacitances it in the form junction capacitance, external-capacitance and also stray capacitance (or) parasitie capacitance.

racles

This

rat

LR-

SB

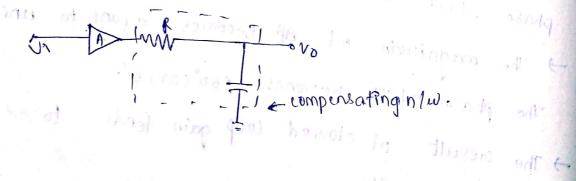

Because of These the op-amp gain decreases at higher frequencies is effect of capacitance is usually taken into account in the high fiequency equalent cht of op-amp by adding a Capacitor in the opposit has shown in the fig.

-> From the ckt we an use only 1 capacitor suchthan it has only one break treatmenty at the man phase shi - 90. However; an op-amp can have several break frequencies such a case many capacitors as there break frequecies suppose we can take e Break frequencies two capacitor are available, man Phase shift [K-186°]

-) Three capacitors are available at 3 braine frequ The man phase shit + 11-270.

corol out or it is interested by out of contribution of the

the rolled date wegines.

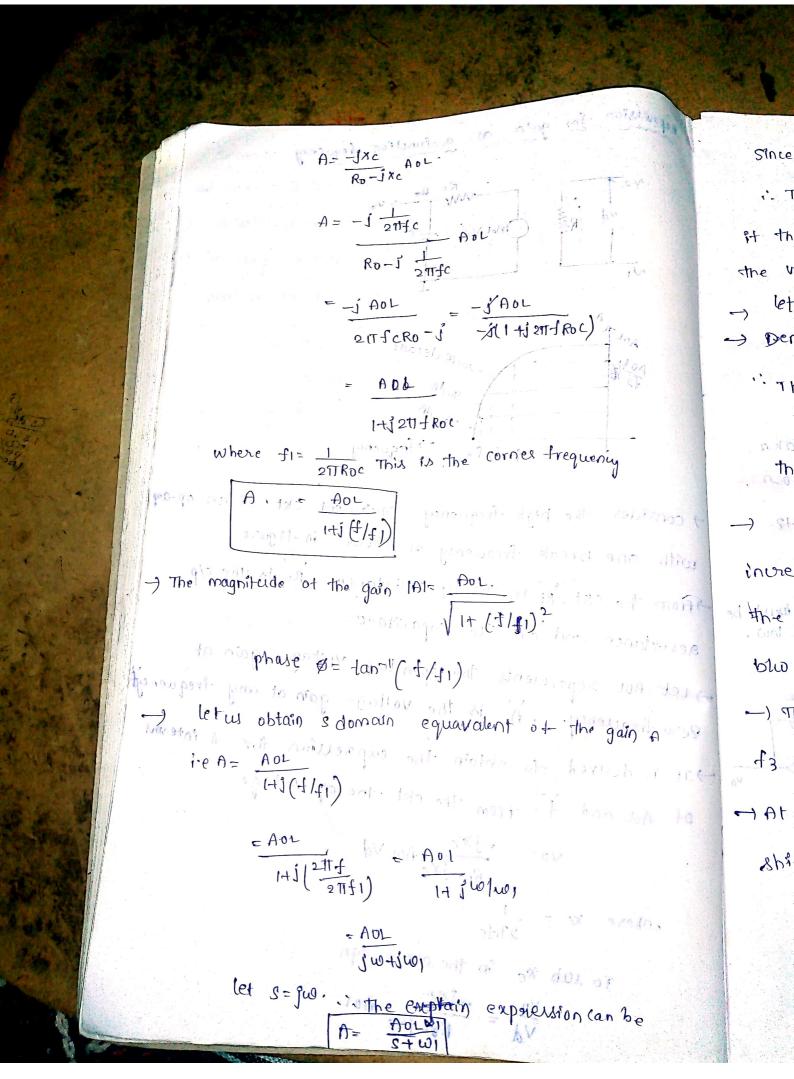

Expression for gain a a function frequency

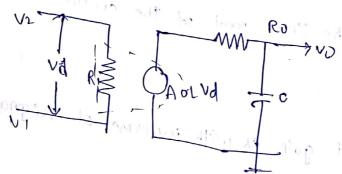

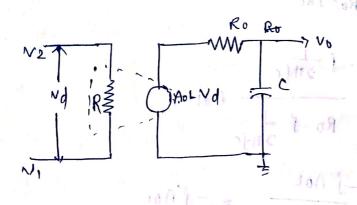

-) consider the high frequency equivalent ckt oil an op-and with one break frequency as shown in figure.

-Afrom the cht hi is the 1/p mesistance Rolls the 0/p assistance and cis the capacitance.

ret ADL Represents the open loop voltage gain at any frequency sero frequency. A is the voltage gain at any frequency s

It is desired to obtain the expression for A internal of AoL and J. From the ckt the old voltage

cohere xc = 1

To sub xc in the above eqn

Vo -JAC

AOL . 20 = 2 19)

2R

St-

2

input

(a)

a

Since there is only one break frequently,

. The voltage transfer function has only one pole, Ft the op-amp has several broak troquencies then

the voltage transfer function having many poles

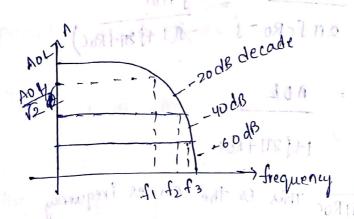

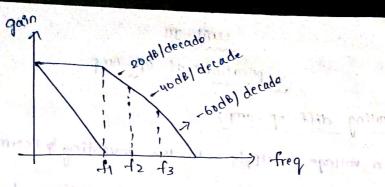

- let there are 3 break frequencies.

- -> Denoted as f1, f2, f3.

"The A.T.F A= ADL COIND, WD3

and of anotheron  $(s+\omega_1)(s+\omega_2)$   $(s+\omega_3)$

the corresponding frequency response as shown in fig.

- -> From the wasig we can observed that frequency increases the Voltage gain de creases blu Flands\_ the gain decreases at the nexte of 20dB per decade blu fi and f3,

- -) The gain at the state of gods per decade beyon of at the nate of 60 dB per decade. 30\_

- At each break frequency causes a man phase shift of -900. blw the ilp and ofp vollages.

Mil

INA

ing cale

(0)

10

12

- Wisolasi

features:

The ip impedence for zctul op-amp is more than looka

2. The old impedence for Icat do amp is below too.

3. The frequency sange of an op-amp is 0-1 mHz.

4. The voltage gain of the ICT41 opramp is above

000,000

5. The offset current and offset voltage of IC 741 must be swol

stability of op-amp !-

path consists a resistor as shown in fight with et his represents open - bop gain op-amp of the and and act represents closed bop gain.

ACL = A 14AB where Bill the Fib factor. est han it all

II a closed loop gain is said to be infinate gain then It AB=0.

1- (-AB)=0

1- (-AB)=0

1- (-AB)=0

1- (-AB)=0

- AB preparements the loop gain where AB is a complex quantity attence in order to satisfy the above Conditions.

- -> The magnitude must an bei unity par a and war betgable éce 11-14 plus juite magnitude alla line

- -> The phase is L-AB =0 cor) integrees multiplies etten

- nature such that II does not produce any phase shift so the op-amp functioning as inverting amplifies then at low frequency their a phase shift of 180° blw 1/p & o/p.

- The higher frequencies each break frequency introduced mark phase shift -90 in open loop gain of ap-amp has a break frequency of total phase shift will be -180.

- The magnitude of -AB becomes equal to unity

The phase shift becomes \$60° (or) 0°.

- -> The gresult of closed loop gain tends to become infinite.

√ .

ka.

\*

Kin'i

bw.

•

rge-

rat

2R

SB

input

(a)

a

Ic : and-tolstity may be setup condition Act > A.

It low frequencies their is no additional phase Shift caused by open loop gain A. and hence np Es positive. This maker ACLCA. which results The operation is quit stable,

→ If a large B.w coupled with closed loop gain hou low is required in any practical application suitable compensation technique must be adopted to parevent intability.

-) The following compensation techniques are generally ewed in order to gate the mole of rate -20dB/decab over a ride range of frequencies 1+2

1. Dominate pole compensating technique 2. pole-zero

Dominate pole comp tech:

In this method the RC N/W is added inscrien with op-amp as shown in fig.

Deceme infaile

By using this technique to get nequired stability but the open loop Bw decrease.

pole -zero comp tech:-

han word in the first

2001)

200 Bldecade 2R

200 Bldecade 2R

200 Bldecade 282

20

rge-

rat

iss

input

(a)

This

added to the T.F by means of new as shown fig

added to the T.F by means of new as shown fig

pesister R1 is in series with the op-amp olp

terminal in the New R2C2 is connected across

the O/P thin tech increases the open loop B.w by

making -20 dB/pecade. slope line passes through

od R line at the cornes frequency for instead of A.

By comparing above two tech it is seen that

their is an increase of open loop B.w. equals to

their is an increase of open loop B.w. equals to

12-f1 by adopting the pole zero compensating tech

instead of dominated pole compensating technique.

instead of dominated pole compensating technique.