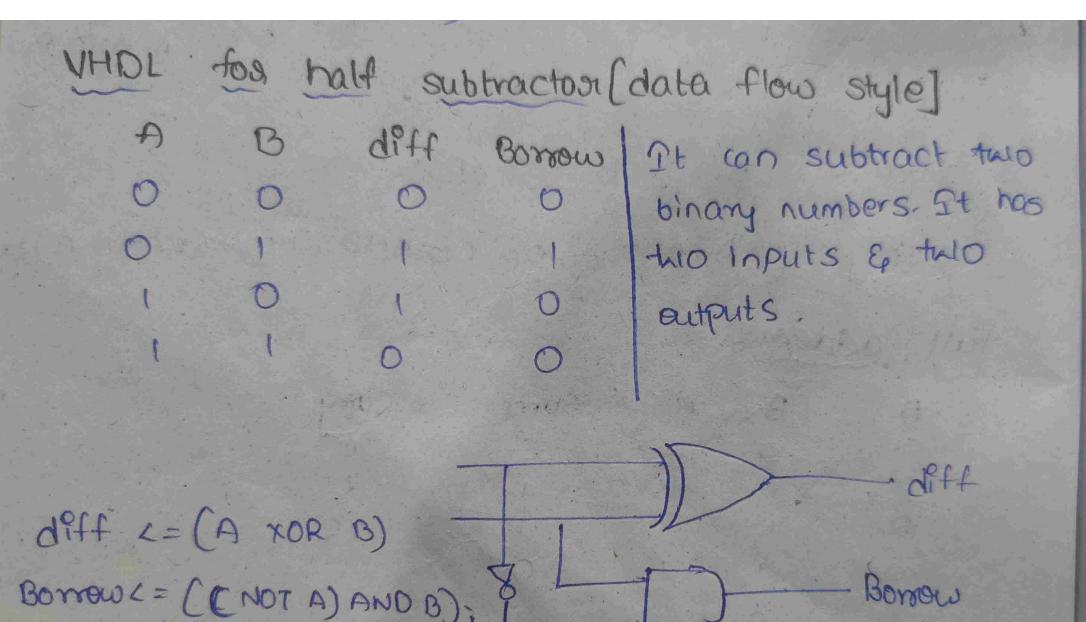

liborary IEEE; use TEEE STO LOGIC - 1164 all; entity and gate is Poort (A, B: in std-logic) Deff, Borrow: out std-logec); end and-gate; Architecture and arch of and gate is begin diff c = (A xOR B), BOMOW L= ( CNOT A) AND B); end and-asich;

function in digital computer

The ALU performs simple addition, subtraction, multiplication, division,

multiplication, division, and logic operations, such as OR and AND. The memory stores the program's instructions and data.

| 2000018-0 | JOP          | uts |    | 1 outputs |  |  |

|-----------|--------------|-----|----|-----------|--|--|

| operation | S-2          | SI  | so | Fig       |  |  |

| clean     | 0            | 0   | 0  | F=0000    |  |  |

| B-A       | 0            | 0   | 1  | 8-A       |  |  |

| A-B       | 0            |     | 0  | A-B       |  |  |

| DOA       | 0            |     |    | A+B+CIN   |  |  |

| XOR       | 1            | 0   | 0  | A YOR B   |  |  |

| ORMON     | 100          | 0   |    | A OR B    |  |  |

| AND       | 1            | 1   | O  | A AND B   |  |  |

| PRESET    | 1            | 1   |    | F=1111    |  |  |

|           | A THE STREET |     |    |           |  |  |

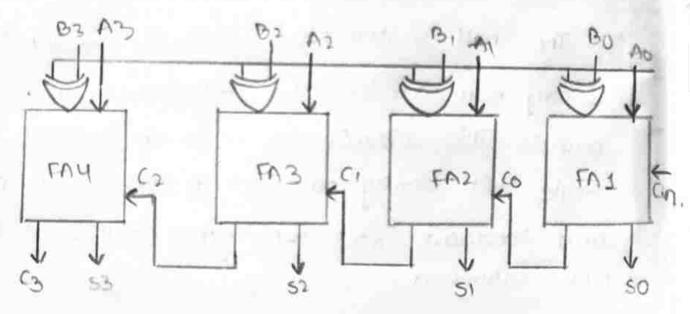

#### Disadvantages of Ripple Carry Adder-

Ripple Carry Adder does not allow to use all the full adders simultaneously.

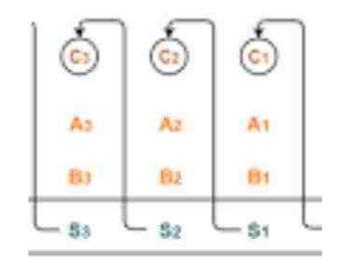

Adding two 4-bit Numbers

- Each full adder has to necessarily wait until the carry bit becomes available from its adjacent full adder.

- This increases the propagation time.

- Due to this reason, ripple carry adder becomes extremely slow.

```

BCD to 7 segment decoder

library IEEE;

USC IEEE - STD-LOGIC - UG4-all;

Entity codeconventer 95

Post (bcd: Pn std-logic-vector (3 downto 0);

Leds: out std-logic-vector (6 down to 0);

code convertes;

end

Architecture codeconverter_auch of codeconverter is

begin

Paocess (BCd)

begin

case bid es

"00000" => leds <="1111110";

when

"0001" =) leds < = "0110000";

when

"0010" => leds c="1101101";

when

"0011" => ledsc=" 1111 001";

when

"0100" => ledsc=" 0110011";

when

"0101" > leds <= "1011011";

iohen

"0110" => leds <=" 011111";

when

"OIII" => leds (=" 111 0000";

when

"1000" => leds c="1111111";

when

"10001" => leds <= " 1111 011";

when

otheass leds c=11_

mhen

end case;

end process;

end code. converter - asch;

```

#### VHDL Code For 4 to 1 Multiplexer

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity mux_4to1 is

port(

A,B,C,D : in STD_LOGIC;

S0, S1: in STD_LOGIC;

Z: out STD_LOGIC

);

end mux_4to1;

architecture bhy of mux_4to1

is

begin

process (A,B,C,D,S0,S1) is

begin

if (S0 = '0' \text{ and } S1 = '0')

then

Z <= A;

elsif (S0 = '1' and S1 =

'0') then

Z <= B;

elsif (S0 = '0' and S1 =

'1') then

Z <= C;

else

Z \leq D:

end if;

end process;

end bhv;

```

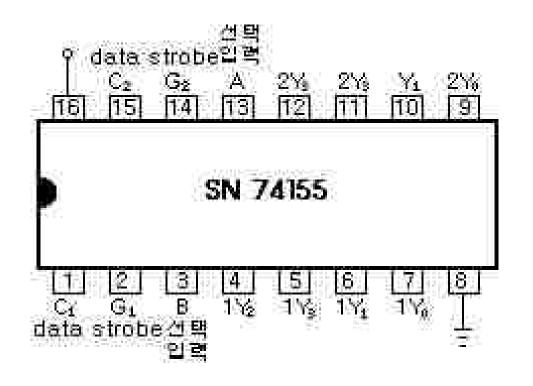

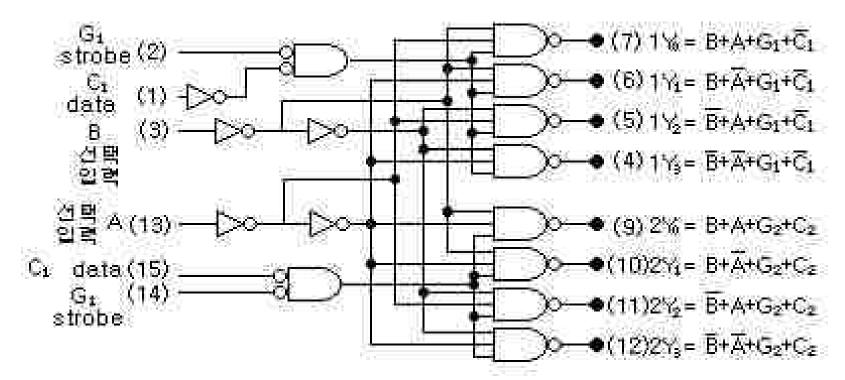

### VHDL Code for 1 to 4 Demux

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity demux_1to4 is

port (

F : in STD_LOGIC;

S0,S1: in STD_LOGIC;

A, B, C, D: out STD_LOGIC

);

end demux_1to4;

architecture bhy of

demux_1to4 is

begin

process (F,S0,S1) is

begin

if (S0 = '0' and S1 = '0')

then

A <= F;

elsif (S0 = '1' and S1 = '0')

then

B \leq F;

elsif (S0 = '0' and S1 = '1')

then

C <= F;

else

D \leq F;

end if;

end process;

end bhv;

```

### Circuit Design of 4 to 16 Decoder Using 3 to 8 Decoder

A decoder circuit of the higher combination is obtained by adding two or more lower combinational circuits. 4 to 16 decoder circuit is obtained from two 3 to 8 decoder circuits or three 2 to 4 decoder circuits.

When two 3 to 8 Decoder circuits are combined the enable pin acts as the input for both the decoders. When enable pin is high at one 3 to 8 decoder circuits then it is low at another 3 to 8 decoder circuit.

## VHDL Code for 4 to 2 encoder using logic gates

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity encoder2 is

port(

a : in STD_LOGIC_VECTOR(3

downto 0);

b : out STD_LOGIC_VECTOR(1

downto 0)

);

end encoder2;

architecture bhy of encoder2

is

begin

b(0) <= a(1) \text{ or } a(2);

b(1) \le a(1) \text{ or } a(3);

end bhv;

```

# VHDL Code for 2 to 4 decoder using logic gates

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity decoder2 is

port

a : in STD_LOGIC_VECTOR(1

downto 0);

b : out STD_LOGIC_VECTOR(3

downto 0)

);

end decoder2;

architecture bhy of decoder2

is

begin

b(0) \ll not a(0) and not

a(1);

b(1) <= not a(0) and a(1);

b(2) \le a(0) and not a(1);

b(3) \le a(0) and a(1);

end bhv;

```

b) Dolan the charcely and explain the operation of binary addes subtractor.

Ans.

A Binary Adders subtraction is one which is capable of both addition and subtraction of binary numbers in one circuit itself. The operation being performed depends upon the binary value the control signal holds It is one of the components of the ALU

This charuit orequires Exor gate, full address, Binary addition and Subtraction

. As shown in fig the first full added has control line diaectly as its input (cin). The input Ao es directly input on FAI. The 3th enput es the exor of Bo and m. The two outputs produced asie so and G It the value of mis 1 the output of BO+BO! Thus the openation would be A+(BO1). Now 2's comp subtraction for two numbers A & B is given by A+B! This suggests that when k=1, the openation being peoformed on the four bit numbers is subtraction

```

posalle Binary Addes subtractors :

REDDONY JEEE;

use IEEE STO-LOGIC-1164.all;

ENRTY PBAS is

Post (A: Pn std-logic - vector (0 to 3);

Bin Std-logic. vector (0 to 3);

CPn, m: In std-logic;

S: out std-logic-vector (0 to 3);

C: out std-logPc-vector (0 to 3));

End PBAS;

Architecture PBAS_agin of PBAS is

signal 00,01,02,03,01,05,06,04: Std-10glc;

component FA

Post (Io, I, Iz: in std-logic.

sum, carry: out std-logic):

End component;

component xDR

Post (I3, Iu: Po std-logic;

Is: but std-logic);

End component;

begin

```

```

postmap(B(0),00,01).

L1: XOR

(2: xOR portmap(B(1),02,03).

13: xOR postmap (B(2), Dy, Ds);

Ly : XOR portmap (B(3), D6, D4).

post map (A(O), D1, (Pn, S(O), C(O));

L5 : FA

portmap (A(1), D3, c(0), s(1), c(1));

FA

L7: FA portmap (A(2), D5, C(1), S(2), C(2));

: FA portmap (A(3), Dq, C(2), S(3), C(3));

End

PBAS-arch;

```

6.1

L8

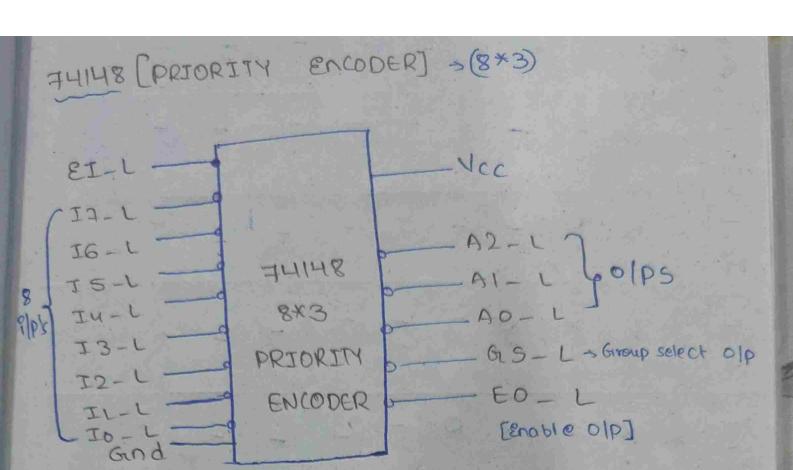

GS\_L[when more than 1 ilp is asserted]

Haz Ia

46 = 16 . Ia!

H5= Is. I61. Ia1

H4= I4. Is1. I61. I21

A2-L= HU+H5+H6+H7 A1-L= H2+H3+H6+H7 A0-L= H1+H3+H5+H7

H3=I3. Iu'. Is'. I6! I71

H2= I2 - J3' エ1 , J5' I6' , Ja1

HI= II. I21. I31. Iu1. I51. I61. I71

HO=IO, I', I2'. I3'. I1'. I5'. I6'. I7'

0

| EI-L     | Jo-1 | 7.      | 14   |      |      | Party of |      | 7 7 10 |      |      | 100  |        | - 1  |

|----------|------|---------|------|------|------|----------|------|--------|------|------|------|--------|------|

| The same |      | ILL     | I2-1 | I3-L | Ju-L | Is-L     | J6-L | Ja-L   | A2-L | AI-L | A0-L | CJ-U-0 | EO-L |

|          | X    | ×       | ×    | ×    | X    | ×        | ×    | ×      | - (  | -    | C    | 18     | 1    |

| 0        | X    | ×       | ×    | ×    | ×    | ×        | ×    | 0      | 0    | 0    | 0    | 0      | 1    |

| 0        | *    | ×       | ×    | ×    | ×    | ×        | 0    |        | 0    | 0    |      | 0      | 1    |

| 0.       | X    | x       | ~    | ×    | ×    | 0        |      | i      | 0    | (    | .0   | 0      | 1    |

| 0        | ×    | ×       | ×    | ×    | 0    |          | 1    | -      | 0    | 1    |      | 0      | 1    |

| 0        | X    | ×       | ×    | 0    | , ,  |          |      |        | (    | 0    | 0    | 0      |      |

| 0        | X    | ×       | Ö    | P    |      | 1        |      |        | 1    | 0    | 1    | 0      |      |

| 0        | x    | 0       | + /  |      |      |          |      |        | 1    | ,    | 0    | 0      |      |

| 0        | 0    |         |      |      |      |          |      | • (    |      |      | 1    | 0      | 11   |

| 0        |      | (   2 . |      |      | (    |          |      |        |      | 1.   | 1-1  | 9      |      |

|          |      |         |      |      |      |          |      |        |      | 1    |      |        | 100  |

```

1969ady JEEF;

USE JEEE STO-LOGIC 1164 all,

Entity proposity-encoded is

Posit (I-1: Po std-logic-vector (+ deconto 0).

EI_L: in std_logic;

A-L: out std-logic-vector (2 down to 0);

GS-L, EO_L: out std-logic);

end priority_encodes;

32 90 0 h 600

Architectuae priority_Encoder-asich of priority_

Encodea ?s

signal EI, EO, GS: Std-logic;

signal A: Std-logic-vector (2 down to 0):="000";

signal I: std-logic-vector (7 dounts 0);

begin

EIC= (not EI-L);

I < = (not I-W;

EO (=11';

GS (= '0';

?f EI='0' then EO <= '0';

else

for i in 7 down to 0 100p

94 I(i) = '11 then

GSC=111:

EOL ='0';

AL = conv-std-logic-vector (j. 0);

```

exit; end Pt; ALLEN BEST ST. end loop; The Last roof to a seen - patte end 94, EO-LC = Chot EOD; 100 ble GIS-LC = Cnot GS) A-L' <= (no 1- A); 100:100:100 15 7 3 3 79 .1 end process; end proority. Encodes auch

555003343

312 11 GO + P3 P2 G1+ P2 G2+ G2 Parogeamo 4-BIT CLA Parogeam (3331 PRODUCT SEEE) Use IEEE. STD-LOGIC-1164 all; 'Entity cla-block is Posit (P.G. : 9n std-logic-vector (3 down to 0); Cen: in std-logic; c: out std-logec-vector (4 down to a)). end cla-block. Architectuse cla-agen of cla-block is began ((0) < = (°) ((1) <= ((P(0) AND (CO)) OR G(0)). c(2) < = ((P(i) AND P(0) AND C(0)) OR (CPW AND G(0)) [3]11] [2014(3-11)] [11] (R GW); C(3) <= ((P(2) AND P(1) AND P(0) AND ((0)) OR ((P(2) ANDP(1) AND G(0)) OR (P(2) AND G(1)) OR G(1));

((4) = ((P(3) AND P(2) AND P(1) AND P(6) AND ((0))

OR (P(3) AND (P(2) AND P(1) AND B(0)) OR

(P(3) AND P(3) AND G(1)) OR (P(3) AND AND (2))

OR (G(3));

4-CLA ADDER PROGRAMS

A[A3 A2 A1 A0] | S B[B3 B2 B1 B0] | Cout

19 baary IEEE; Use IEEE. STD-LOGIC-1164.all; Entity added 95

Posit (A, B: in std-logic-vector (3 down to 0);

Co : 9n std-logic;

s: out std-logic\_vector(3 down to 0);

Cout: out std-logic).

end addess;

Architecture addess arch of addess is

signal p, q: std-logic-vector (3 downto 0):="0000;

signal C: std-logic-vector (4 downto 0):="0000";

component cla-block

Port (P,G: in std-logic-vector (3 down to 0);

(9n: in std-logic;

end component;

begin

PC=(A YOR B).

GL = (A AND B);

L1: cha-block posit map (P, G, G, C);

S <= (P xOR C (3 down to 0)),

Cout < = ((u);

end addeq asch;

#### a) 2-INPLIT 4-RIT MULTIPLEXER

The MSI, 74X157 is a 2-input, 4-bit Multiplexer. This multiplexer has two sets of 4-bit inputs. It also has 4-bit outputs. The single select input line allows the first set of four inputs or the second set of 4-inputs to be connected to the output. Thus four-bits of data from two sources are routed to the output. The function table and the circuit of the multiplexer are shown, table 18.1, figure 18.1

The multiplexer has two sets of 4-bit active-high inputs 1A, 2A, 3A, 4A and 1B, 2B, 3B, 4B respectively. The multiplexer has 4-bit active-high outputs 1Y, 2Y, 3Y 4Y. The single select input allows either the 4-bit input A or the 4-bit input B to be connected to the 4-bit output Y. The G active-low pin enables or disables the Multiplexer.

### 74157 [MULTIPLEXER]

| En     | 74157 |               | Inp  | uts | Output          |  |  |  |

|--------|-------|---------------|------|-----|-----------------|--|--|--|

| 100    |       |               | En-1 | S   | 14 27 37 47     |  |  |  |

| (D)    | 14    | - } Y [4-bits | 7/1  | ×   | 0000            |  |  |  |

| 200    | 24    | - [X [4-010   | 0    | 0   | 100 200 300 400 |  |  |  |

| 300    | 44    |               | 0    |     | 101 201 30, 401 |  |  |  |

| - 1401 |       |               | 201  |     |                 |  |  |  |

19 beauties; USC IEEE STO LOGIC -1164 all, Entity mux is Post (En\_l: in std-logic) s: in std-logic; Y: out std-logic-vector (3 down to o). AB: " std: logic-vector (3 down to o)). end mux; Architectuse mux-asch of mux is signal K: std-logic-vector (3 down to 0); begin with s select k C= A when 'o'. B when '11, other others; Y <= K when En.1='0' else Y <= "000"; end mun;

```

XOR Gates

IPbaany IEEE;

USC IEEE. STD_ LOGIC_ 1164.all;

Entity xor-gate 93

Post CA, B: in std-ogic;

c: out std-logic);

end xor-gate;

Architecture xor-asion of xor gate is

begin

C (=(A XOR B);

end xor-asch;

NOT gates

196 early IEEE;

USC IEEE STD-LOGIC-1164 all;

Entity NOT-gate is

Posit (D: 90 std-logic;

y out std-logic).

end nor-gate;

Architecture NOT-agen of not gate is

begin

Y L = (NOT D);

end not-asich;

```

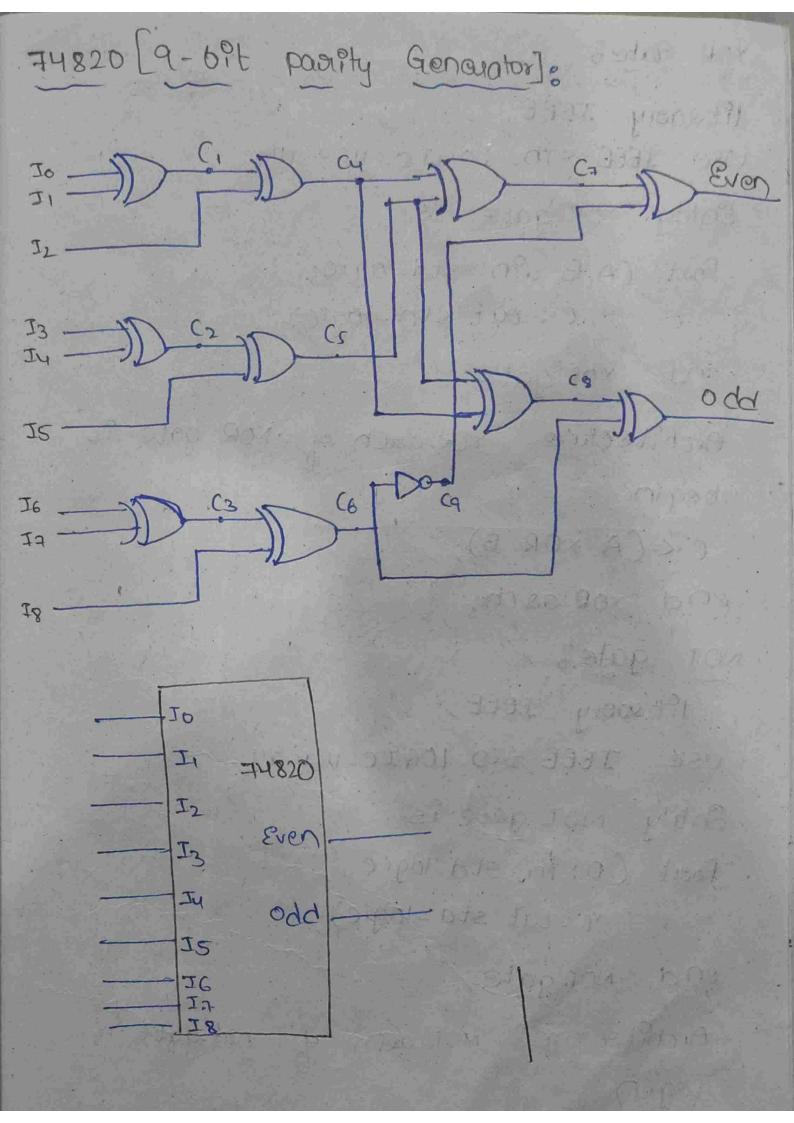

```

Phany IEEE;

USE TEEE. STO_LOGIC_ 1164, all;

Entity 9-6it posity is

Posit (I: in std-logic-vector(8 down to 0);

Even, odd: out std-10gic);

end q-bit pasity;

Architecture passity—asich of 9-bitposity is

signal c: std-logic-vector ( downto );

component xor-gate

Posit (AB: in std-1091C;

c: out std-logic);

end component;

component NOT gate

Poat (0: in std_ logic;

ye out std-logic);

end component;

pegin

L1: xORI posit map (ICO), ICI), CCI);

(2: x0R2 posit map (I(3), I(4), C(2));

13: x0R3 posit map (IC6), IC7) ((3)).

Ly: xORy post map (CCI), I(2), C(4));

LS: xORT port map (CC2), ICS), CC5);

L6: xOR 6 port map (C(3), I(8), C(6));

L7: XOR7 port map (CCW), CCT), C(7));

```

port map (c(4), c(5), c(8)). L8: XOR8 L9: NOT 1 port map (((6), ((9)); post map (CC7), CC9), even). LIO: XOR 9 (111 : x0R10 post map (cc(8), cc(6), odd); painty asch;

### VHDL Code for 2 to 4 decoder using case statement

```

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity decoder is

port (

a : in STD_LOGIC_VECTOR(1

downto 0);

b : out STD_LOGIC_VECTOR(3

downto 0)

) ;

end decoder;

architecture bhy of decoder

is

begin

process(a)

begin

case a is

when "00" => b <= "0001";

when "01" => b <= "0010";

when "10" => b <= "0100";

when "11" => b <= "1000";

end case;

end process;

end bhv;

```